第二节 计算机的基本组成

1.冯诺依曼计算机的特点

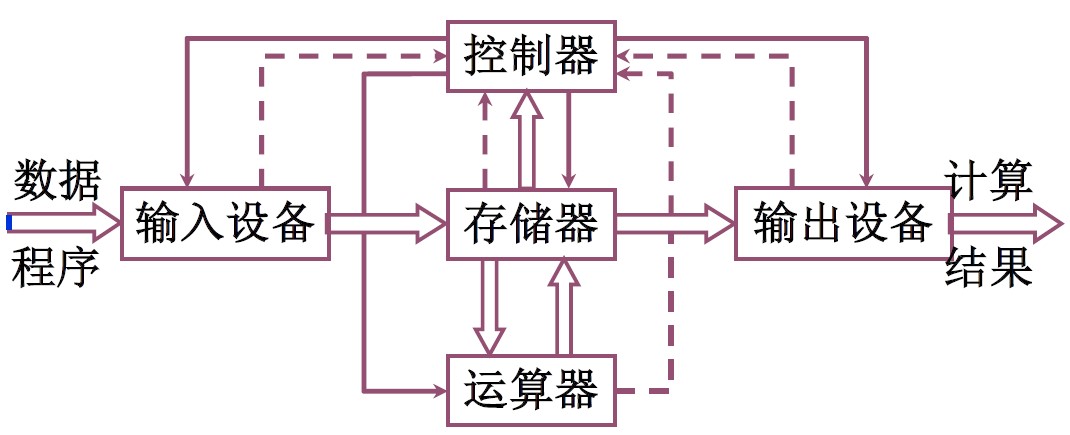

(1)计算机由五大部件组成:运算器、存储器、控制器、输入设备、输出设备。

(2)指令和数据以同等地位存于存储器,可按地址寻访;

(3)指令和数据用二进制表示;

(4)指令由操作码和地址码组成;

(5)存储程序;

(6)以运算器为中心。

图1 冯诺依曼结构(实线是数据传输,虚线是地址传输)

2.硬件系统的改进

问题1:以运算器为中心,导致运算器成为系统的瓶颈。

问题2:不具有层次化的特征。

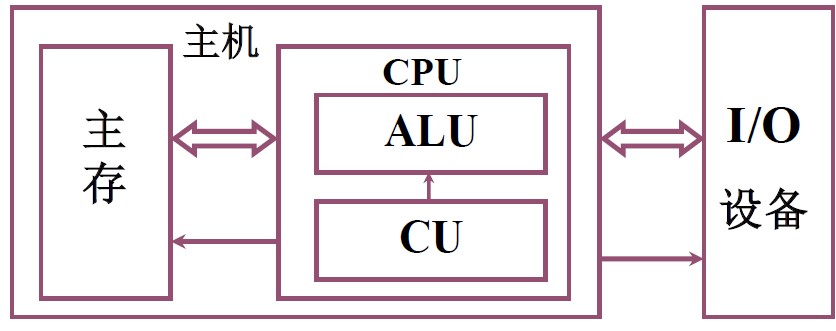

改进1:以存储器为中心的计算机硬件框图

图2 以存储器为中心的计算机硬件框图

改进2:

运算器 ALU ---------CPU-----------主机

控制器 CU ----|

存储器 -------主存----------------|

---|辅存

输入设备-------I/O设备

输出设备-------|

图3 改进2的计算机硬件框图(现代计算机硬件框图)

系统复杂性管理方法2(3Y)

1.层次化(Hierachy):将被设计的系统划分为多个模块或者子模块;

2.模块化(Modularity):有明确定义(well-defined)的功能和接口;

3.规则性(regularity):模块更容易被重用。

3.计算机的工作步骤

3.1上机前的准备

①建立数学模型

②确定计算方法

③编织解题程序:程序-运行的全部步骤;指令-每一个步骤。

编程举例:

计算ax2+bx+c

假设系统包含加法指令、乘法指令、取数指令、存数指令、打印指令和停机指令。

假设a,b,c已经保存起来了。计算步骤如下:

①首先取x至运算器中的累加器(寄存器)中;(取数指令)

②乘x,在运算器中,计算的x的平方,保存在累加器ACC中;(乘法指令)

③乘a,在运算器中,在累加器ACC中保存ax的平方;(乘法指令)

④存数指令,存ax的平方在存储器中;(存数指令)

⑤取b至运算器中;(取数指令)

⑥在运算器中,对b乘x,acc中保存bx;(乘法指令)

⑦把bx+ax2,在累加器中;(加法指令)

⑧加c,在累加器中;(加法指令)

一共执行8条指令,指令较多,运算速度慢存储量较大。但是如果做一个优化,将该式处理为(ax+b)x+c。计算步骤如下:

①取x至运算器中;(取数指令)

②a乘x,在运算器中;(乘法指令)

③把ax+b,在运算器中;(加法指令)

④乘x,在运算器中;(乘法指令)

⑤加c,在运算器中。(加法指令)

一共执行5条指令,相对来说指令少,运算速度快,存储量也小。

另外要说明的是,累加器是运算器的一个部分。

指令格式举例

| 操作码 | 地址码 |

取数(把内存单元α中的数据存储在ACC中) [α]àACC

假设我们的指令有16位,操作码为6位,地址码为10位。则可以如下格式:

000001 0000001000

存数(把ACC中的数据保存在内存单元β当中) [ACC]àβ

加 γ [ACC]+[γ]àACC

乘 σ [ACC]×[σ]àACC

打印 θ [θ]à打印机

停机

假设内存和ACC均为8位长度,那么乘法会使数据边长,必然会导致数据溢出。应予以注意。

计算ax2+bx+c程序清单如下图所示。

图4 计算程序清单(x/a/b/c/存储结果均为二进制数存储)

冯诺依曼机中,指令和数据都是同等地位以二进制数据保存起来的。

3.2 计算机的解题过程

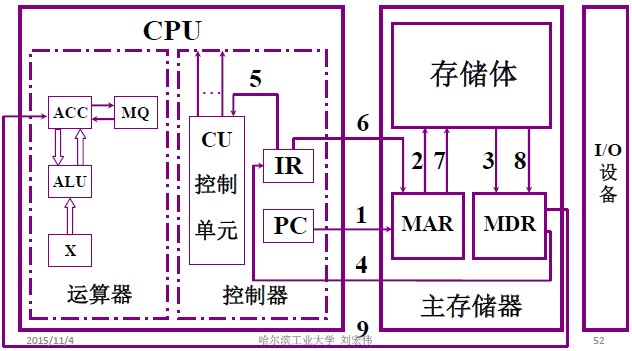

(1)存储器的基本组成

图5 存储器的基本组成

存储器-存储单元-存储元件(0/1,),类似于大楼-房间-床位(无人/有人)

存储单元:用来存放一串二进制代码;

存储字:存储单元中二进制代码的组合;

存储字长:存储单元中二进制代码的位数。

每个存储单元赋予一个地址号,实行按地址寻访。

MAR(Memory Address Register):存储器地址寄存器。反映存储单元的个数。

MDR(Memory Data Register):存储器数据计算器。反映存储的字长。

设MAR=4位,MDR=8位,则存储单元是16个(24),存储字长为8。

(2)运算器的基本组成及操作过程

图6 运算器各部分组成及功能

运算器核心是算术逻辑单元(ALU),它是一个组合逻辑电路,也就是说当输入撤销之后,输出也会消失,因此后面需要存在一个寄存器,保存参与运算的数据,这两个寄存器为ACC(累加器)和X(数据寄存器)。如果做乘法运算,则多余出来的位数存放在MQ中。

注意:此结构仅限于本课程的一种类型。

对于加法来说,加数存放在X中,被加数存放在ACC中,和存放在ACC中;对于剪发说,被减数存在ACC中,减数存在X中,差在ACC中;对于乘法来说,乘法可以用加法和移位的方式来计算,被乘数存放在X中,乘数放在MQ中,乘积高位在ACC中,乘积地位在MQ中;对于除法来说,除法是用减法和移位来实现的,被除数在ACC,除数是X中,商在MQ中,余数在ACC中。

①加法操作过程

指令:

| 加 | M |

初态:ACC 被加数

第一条指令:[M]àX

执行加法指令:[ACC]+[M]àACC

如图7所示。

图7 加法(减法)操作过程图

②减法操作过程

指令:

| 减 | M |

初态: ACC中存在被减数

第一条指令:[M]àX

执行减法指令:[ACC]-[X]àACC

③乘法操作过程

指令

| 乘 | M |

初态 ACC 被乘数

第一条指令(乘数):[M]àMQ

第二条指令(被乘数):[ACC]àX

第三条指令(累加之前先将ACC置零):0àACC

乘法指令(累加+移位):[X]×[MQ]àACC//MQ(高位//地位)

只有ACC送到X以后才可以做乘法,才能把0送到ACC中。但是第一条指令和第二条指令顺序可以互换。这个先后顺序是控制器来控制的。

图8 乘法(除法)操作过程

④除法操作过程

指令

| 除 | M |

初态 ACC 被除数

第一步指令:[M]àX

第二步指令:[ACC]÷[X]àMQ

(余数在ACC中)

MQ又叫乘商寄存器。注意:[X]指的是X对应地址的内容。

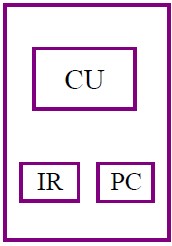

(3)控制器的基本组成

控制器的功能:解释指令(从取指令、分析指令、取操作数……一直到完成指令);保证指令按序执行。

完成一条指令包括三步:①取指令PC(程序寄存器);②分析指令IR(指令寄存器);③执行指令CU。

PC中存放当前要执行指令的地址,指令地址是相邻的,因此PC具有计数功能,即把PC+1赋给PC。

IR存放当前欲执行的指令,控制单元可以把IR中的操作码取出来分析。操作控制就是CU完成。

具体框图如下:

图9 控制器的组成

(4)主机完成一条指令的过程

①以取数指令为例

图10 取数指令的过程

第一步:取指令。要执行指令的地址是PC中,指令存在存储体中。首先PC把地址给MAR,然后给存储体,在控制器控制下,存储体中存储的指令取出来送入MDR中,然后当前指令的地址存在IR中,取指令完成。

第二步:分析指令。把IR中的指令的操作码部分送入CU,译码之后进行下面的操作。

第三步:执行指令。在控制器的控制之下,要把IR指令当中的地址部分送给存储器(MAR),以便取出数据。然后MAR把地址送给存储体重,存储体把数送入MDR,然后送入ACC。

②以存数指令为例

图11 存数指令的过程

第一步:取指令。首先PC把当前指令的地址发送给MAR,然后MAR又发送到存储体,在控制器控制下,存储体中存储的指令取出来送入MDR,MDR将该指令存入IR之中。

第二步:分析指令。把IR中的指令的操作码送给CU,由CU对指令进行分析,CU发出响应控制信号。

第三步:执行指令。首先在CU控制下,把IR中的指令的地址码送入MAR中,MAR送入存储体,告诉存储体现在有一个数据要存进来和地址是多少。然后在CU控制下,ACC中的数据被送入到MDR中,然后再送入到存储体中,在存储体中的地址按照MAR的要求来确定。

(5)ax2+bx+c程序的运行过程

①将程序通过输入设备送至计算机。

②程序首地址送入PC中。

③启动程序运行:

取指令PCàMARàMàMDRàIR,(PC)+1àPC

分析指令:OP(IR)àCU(OP是操作码)

执行指令:加:Ad(IR)àMARàMàMDRàACC。(Ad代表地址码的意思)

④打印结果

⑤停机

文章评论